# THE 99000 MICROPROCESSOR

# THE 99000 MICROPROCESSOR

Focusing on the 99000 family of 16-bit microprocessors from Texas Instruments, this book is for anyone involved in designing electronic systems with microprocessors and microcomputers. It stresses the three primary areas in which a thorough background is needed; microcompute architecture, microcomputer software, and hardware interface techniques

The advent of 16-bit microprocessor technology has led to the introduction of newer system concepts, such as pipelining, instruction prefetch, microcoding, illegal instruction detection, macroinstruction emulation, user and supervisor modes of operation, bus demultiplexing, memory paging, memory segmentation, memory mapping, error detection and correction, and cache memory—all of which are discussed in this book.

This book also includes topics common to 8-bit microprocessor technology, such as microprocessor internal architecture, microcomputer system architecture, instruction execution, addressing modes, instruction set, programming techniques, bus cycles, program and data storage memory subsystems, input/output circuitry, and interrupt processing.

HE 99000 MICROPROCESSOR

S

### **CONTENTS**

#### Preface ix

- 1 Introduction to Microprocessors and Microcomputers 1

- 1.1 Introduction 1

- 1.2 The Digital Computer 2

- 1.3 Mainframe Computers, Minicomputers, and Microcomputers 3

- 1.4 Hardware Elements of the Digital Computer System 8

- 1.5 General Architecture of a Microcomputer System 9

- 1.6 Types of Microprocessors and Single-Chip Microcomputers 12

- 2 The 99000 Microprocessor 16

- 2.1 Introduction 16

- 2.2 The 99000 Microprocessor 16

- 2.3 Block Diagram of the 99000 Microprocessor 18

- 2.4 Internal Architecture of the 99000 Microprocessor 25

- 2.5 Execution of an Instruction 32

| 3 | 9900   | 0 Microprocessor                                     |

|---|--------|------------------------------------------------------|

|   | Progr  | amming I 40                                          |

|   | 3.1    | Introduction 40                                      |

|   | 3.2    | Software Model of the 99000 Microprocessor 41        |

|   | 3.3    | Assembly Language and Machine Language 44            |

|   | 3.4    | Instruction Execution Notations 47                   |

|   | 3.5    | Addressing Modes 49                                  |

|   | 3.6    | Instruction Set 64                                   |

|   | 3.7    | Data-Transfer Instructions 64                        |

|   | 3.8    | Arithmetic Instructions 70                           |

|   | 3.9    | Logic Instructions 81                                |

|   | 3.10   | Shift Instructions 85                                |

|   |        |                                                      |

| 4 | 9900   | ) Microprocessor                                     |

|   | Progr  | amming II 93                                         |

|   | 4.1    | Introduction 93                                      |

|   | 4.2    | Compare Instructions 93                              |

|   | 4.3    | Jump Instructions 97                                 |

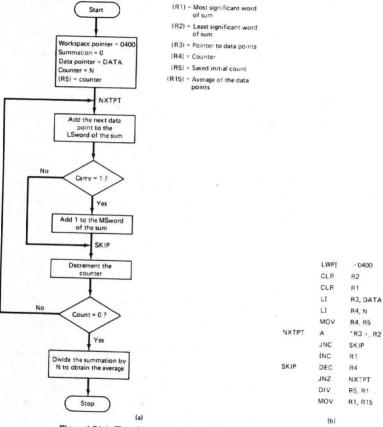

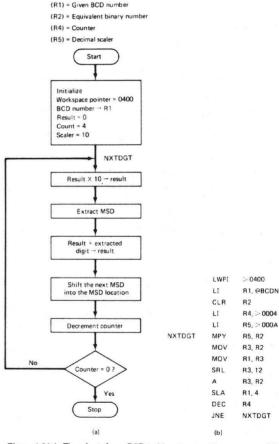

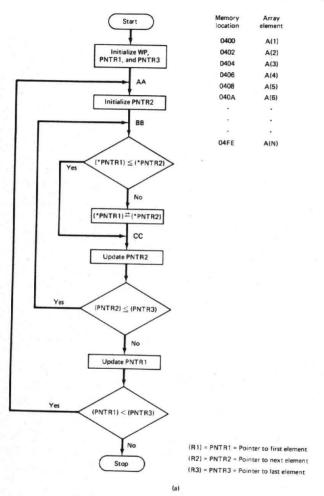

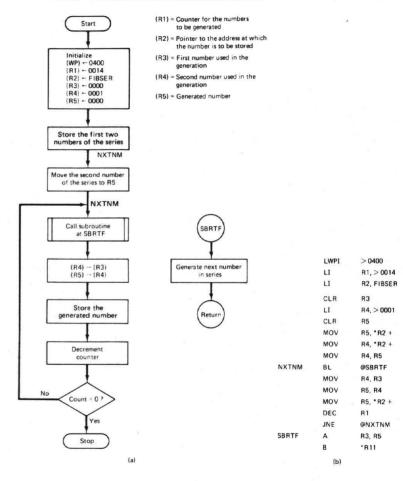

|   | 4.4    | Program Examples Involving Loops 103                 |

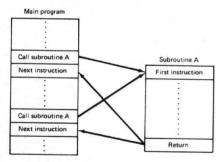

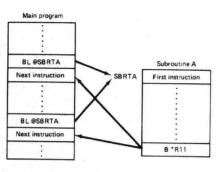

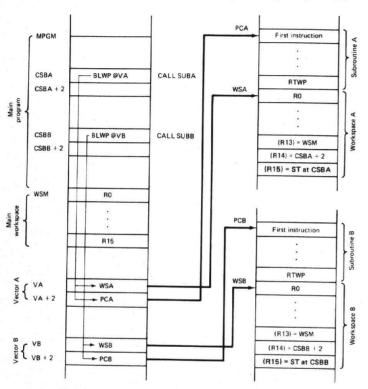

|   | 4.5    | Subroutines and Subroutine Handling Instructions 112 |

|   |        |                                                      |

| 5 |        | ry Interface                                         |

|   | of the | 99000 121                                            |

|   | 5.1    | Introduction 121                                     |

|   | 5.2    | Memory Interface Block Diagram 122                   |

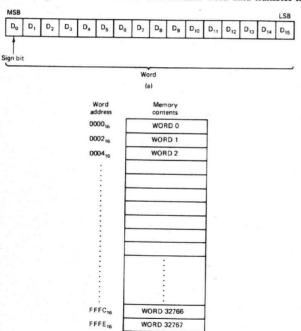

|   | 5.3    | Address Space 122                                    |

|   | 5.4    | Data Organization 124                                |

|   | 5.5    | Dedicated and General Use of Memory 126              |

|   | 5.6    | Memory Bus Status Codes                              |

|   |        | and Memory Control Signals 127                       |

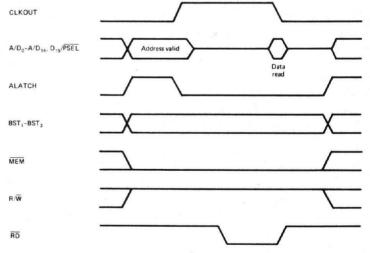

|   | 5.7    | Read Cycle 129                                       |

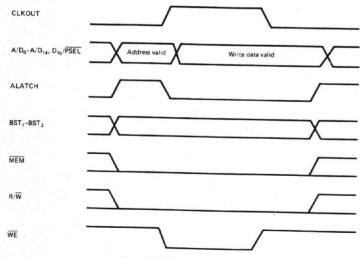

|   | 5.8    | Write Cycle 130                                      |

|   | 5.9    | Slow Memory Interface 131                            |

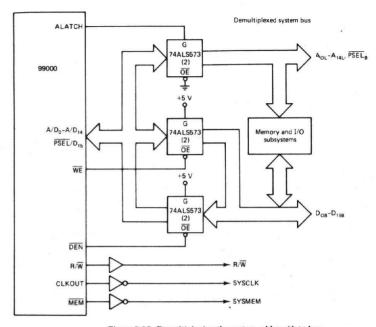

|   | 5.10   | Demultiplexing the 99000's System Bus 132            |

|   | 5.11   | EPROM/Static RAM Memory Subsystem 135                |

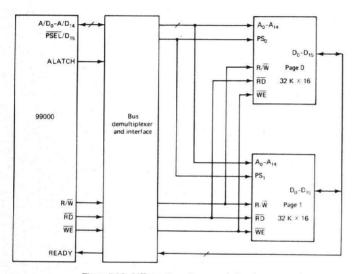

|   | 5.12   | Extending the Address Space of the 99000 135         |

|   | 5.13   | 99000 Memory Subsystem with Error                    |

|   |        | Detection and Correction 138                         |

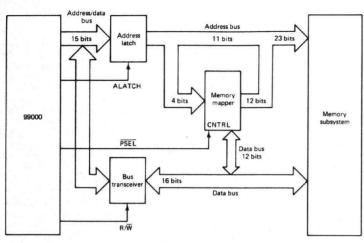

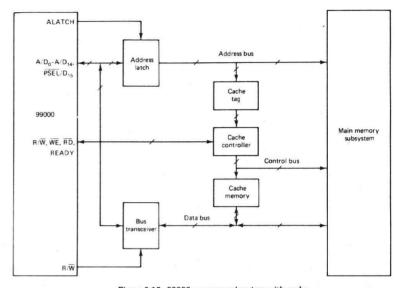

|   | 5.14   | Cache Memory for the 99000 System 140                |

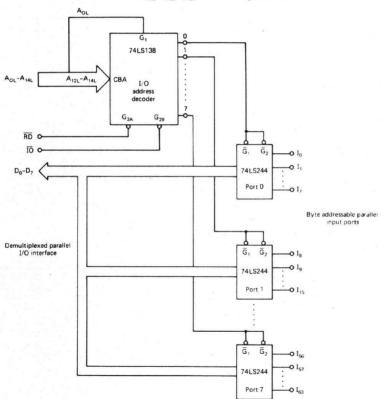

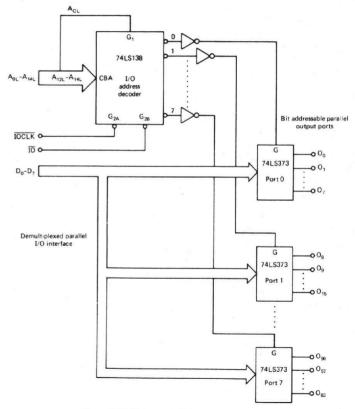

| 6 | Input | t/Output Interfaces                           |

|---|-------|-----------------------------------------------|

|   | of th | e 99000 144                                   |

|   | 6.1   | Introduction 144                              |

|   | 6.2   | Communications Register Unit 144              |

|   | 6.3   | Input/Output Instructions 146                 |

|   | 6.4   | The Base Address and I/O Address Space 147    |

|   | 6.5   | Bit-Serial I/O Operation and Bus Cycle 150    |

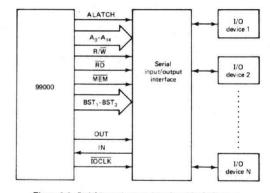

|   | 6.6   | External Serial I/O Interface Circuitry 153   |

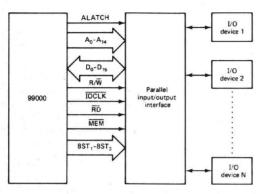

|   | 6.7   | Parallel I/O Operation and Bus Cycle 157      |

|   | 6.8   | External Parallel I/O Interface Circuitry 159 |

|   | 6.9   | Wait States in the I/O Bus Cycle 162          |

7

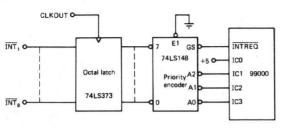

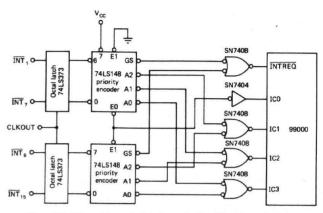

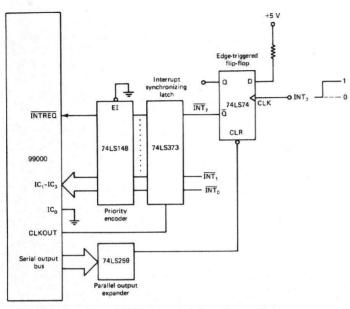

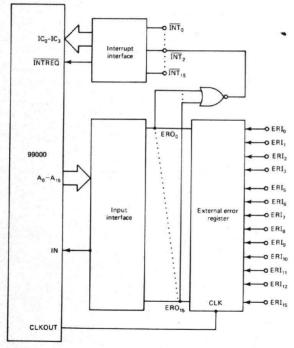

#### Interrupt Interface of the 99000 165 7.1 Introduction 165 7.2 Interrupts 166 External Interrupt Interface 166 Interrupt Priority Levels 167 External Interrupt Request 168 7.6 Priority Encoder 168 7.7 Context Switch Sequence 169 Interrupt Vectors and the Interrupt Vector Table 171 7.9 Interrupt Mask 172 7.10 Reset Interrupt 174 7.11 Nonmaskable Interrupt 175 7.12 External Interrupt Interface Circuitry 175 7.13 Extended Operation Instructions 178 7.14 Internal Interrupt Functions 179 7.15 Illegal Opcode Detection; Macroinstruction Detection and Emulation 181 7.16 Privileged Mode 188 7.17 Arithmetic Fault Detection 190

Bibliography 194

Index 195

### **PREFACE**

One of the most highly visible types of products in the semiconductor marketplace today is the 16-bit microprocessor. Five major 16-bit processor families are currently available: the 99000 from Texas Instruments, the 8086 from Intel, the 68000 from Motorola, the Z8000 from Zilog, and the 16000 from National Semiconductor. These manufacturers are presently in competition to establish market share in the 16-bit marketplace. This book focuses on just one of the newest of these products, the 99000 family of 16-bit microprocessors from Texas Instruments.

Everyone involved in the design of electronic systems involving microprocessors and microcomputers must have a thorough knowledge of three

primary areas: microcomputer architecture, microcomputer software, and

hardware interface techniques. However, most of the books presently available on the subject stress the architecture of microprocessors, their instruction sets, and programming techniques. Typically, very little information is

provided on hardware design and interface techniques. This leaves a gap in

one's understanding of how a microprocessor interacts and interfaces with

its memory and I/O subsystems. This information is the key to successful

application of microcomputer systems. This book closes the gap between the

study of microprocessors and microcomputer systems by putting equal emphasis on the subjects of microprocessor architecture, assembly language

programming, and hardware interface techniques.

The material presented in the book includes topics common to 8-bit microprocessor technology, such as microprocessor internal architecture.

microcomputer system architecture, instruction execution, addressing modes, instruction set, programming techniques, bus cycles, program and data storage memory subsystems, input/output circuitry, and interrupt and exception processing. However, the advent of 16-bit microprocessor technology has led to the introduction of newer system concepts, such as pipelining, instruction prefetch, microcoding, illegal instruction detection, macroinstruction emulation, user and supervisor modes of operation, bus demultiplexing, memory paging, memory segmentation, memory mapping, error detection and correction, and cache memory. Detailed coverage of these more modern topics is also provided in this book.

Use of the book does require some prior knowledge of basic digital electronics. This background is at a level consistent with but not necessarily as extensive as the material covered in earlier Prentice-Hall books: Integrated Digital Electronics, Walter A. Triebel, 1979, and Handbook of Semiconductor and Bubble Memories, Walter A. Triebel and Alfred E. Chu, 1982.

We would like to express special appreciation to Dr. Jerry Van Aken for his worthwhile input on the 99000 microprocessor.

Every effort has been made to provide up-to-date information on the devices covered in the book. However, it is recommended that readers check with the manufacturer for the most recent data.

AVTAR SINGH WALTER A. TRIEBEL 1

# INTRODUCTION TO MICROPROCESSORS AND MICROCOMPUTERS

#### 1.1 INTRODUCTION

The most recent advances in computer system technology have been closely related to the development of high-performance 16-bit microprocessors and their microcomputer systems. During the last three years, the 16-bit microprocessor market has matured significantly. Today, several complete 16-bit microprocessor families are available. They include support products such as large-scale-integrated peripheral devices, development systems, emulators, and high-level software languages. Over the same period of time, these higher-performance microprocessors have become more widely used in the design of new electronic equipment and computers.

This book represents a detailed study of one of the newest 16-bit microprocessors, the 99000 from Texas Instruments. In this chapter we begin our study of microprocessors and microcomputers. The following topics are discussed:

- 1. The digital computer

- 2. Mainframe computers, minicomputers, and microcomputers

- 3. Hardware elements of the digital computer system

- 4. General architecture of a microcomputer system

- 5. Types of microprocessors and single-chip microcomputers

#### 1.2 THE DIGITAL COMPUTER

As a starting point, let us consider what a *computer* is, what it can do, and how it does it. A computer is a digital electronic data processing system. Data are input to the computer in one form, processed within the computer, and the information that results is either output or stored for later use. Figure 1.1 shows a modern computer system.

Introduction to Microprocessors and Microcomputers

Figure 1.1 Modern large-scale computer. (Courtesy of International Business Machine Corp.)

Computers cannot think about how to process data that were input. Instead, the user must tell the computer exactly what to do. The procedure by which a computer is told how to work is called *programming* and the person who writes programs for a computer is known as a *programmer*. The result of the programmer's work is a set of instructions for the computer to follow. This is the computer's *program*. When the computer is operating, the instructions of the program guide it step by step through the task that is to be performed.

For example, a large department store can use a computer to take care of bookkeeping for its customer charge accounts. In this application, data about items purchased by the customers, such as price and department, are entered into the computer by an operator. These data are stored in the computer under the customer's account number. On the next billing date, the data are processed and a tabular record of each customer's account is output by the computer. These statements are mailed to the customers in the form of bills.

In a computer, the program controls the operation of a large amount of electronic circuitry. It is this circuitry that actually does the processing of data. Electronic computers first became available in the 1940s. These early computers were built with vacuum-tube electronic circuits. In the 1950s, a second generation of computers was built. During this period, transistor electronic circuitry, instead of tubes, was used to produce more compact and more reliable computer systems. When the integrated circuit (IC) came into the electronic market during the 1960s, a third generation of computers appeared. With ICs, industry could manufacture more complex, higher-speed, and very reliable computers.

Today, the computer industry is continuing to be revolutionized by the advances made in integrated-circuit technology. It is now possible to manufacture large-scale integrated circuits (LSI) that can form a computer with just a small group of ICs. In fact, in some cases, a single IC can be used. These new technologies are rapidly advancing the low-performance, low-cost part of the computer marketplace by permitting simpler and more cost effective designs.

### 1.3 MAINFRAME COMPUTERS, MINICOMPUTERS, AND MICROCOMPUTERS

For many years the computer manufacturers' aim was to develop larger and more powerful computer systems. These are what are known as large scale or mainframe computers. Mainframes are always general-purpose computers. That is, they are designed with the ability to run a large number of different types of programs. For this reason, they can solve a wide variety of problems.

For instance, one user can apply the computer in an assortment of scientific applications where the primary function of the computer is to solve complex mathematical problems. A second user can apply the same basic computer system to perform business tasks such as accounting and inventory control. The only difference between the computer systems used in these two applications could be their programs. In fact, today many companies use a single general-purpose computer to resolve both their scientific and business needs.

Figure 1.1 is an example of a mainframe computer manufactured by International Business Machines Corporation (IBM). Because of their high cost, mainframes find use only in central computing facilities of large businesses and institutions.

The many advances that have taken place in the field of electronics over the past two decades have led to rapid advances in computer system technology. For instance, the introduction of small-scale integrated circuits (SSIs), followed by medium-scale integrated circuits (MSIs) and large-scale integrated circuits (LSIs), has led the way in expanding the capacity and performance of the large mainframe computers. But at the same time, these advances have also permitted the introduction of smaller, lower-performance, lower-cost computer systems.

As computer use grew, it was recognized that the powerful computing capability of a mainframe was not needed by many customers. Instead, easier access to a machine with smaller capacity was required. It was for this reason that the *minicomputer* was developed. Minicomputers, such as that shown in Fig. 1.2, are also digital computers and are capable of performing the same basic operations as the earlier, larger systems. However, they are designed to provide a smaller functional capability. The processor section of this type computer is typically manufactured using SSI and MSI electronic circuitry.

Figure 1.2 Minicomputer system. (Courtesy of Texas Instruments, Incorporated.)

Minicomputers have found wide use as general-purpose computers, but their lower cost also allows their use in dedicated applications. A computer used in a dedicated application represents what is known as a special-purpose computer. By "special-purpose computer" we mean a system that has been tailored to meet the needs of a specific application. Examples are process control computers for industrial facilities, data processing systems for retail stores, and medical analysis systems for patient care. Figure 1.3 shows a minicomputer-based retail store data processing system.

The newest development in the computer industry is the microcomputer. The microcomputer represents the next step in the evolution of the

Figure 1.3 Point-of-sale system. (Courtesy of Sweda International, Inc.)

computer. It is designed to be smaller and to provide less capability than a minicomputer, at a much lower cost.

The heart of the microcomputer system is the *microprocessor*. A microprocessor is a general-purpose processor built into a single IC. It is an example of an LSI device. Together with the use of LSI circuitry in the microcomputer have come the benefits of smaller size, lighter weight, lower cost, reduced power requirements, and higher reliability.

The low cost of microprocessors, which can be as low as \$1, has made possible the use of computer electronics in a much broader range of products. Figures 1.4 and 1.5 show some typical systems in which a microcomputer is used as a special-purpose computer.

Microcomputers are also finding wide use as general-purpose computers. Figures 1.6 and 1.7 show examples of a home computer and a personal computer. In fact, microcomputer systems designed for the high-performance end of the microcomputer market are rivaling the performance of the lower-performance minicomputers and at much lower cost to the user.

Figure 1.4 Calculator. (Courtesy of Texas Instruments, Incorporated.)

Figure 1.5 Electronic toy. (Courtesy of Texas Instruments, Incorporated.)

Figure 1.6 Home computer. (Courtesy of  $Texas\ Instruments,\ Incorporated.$ )

Figure 1.7 Personal computer. (Courtesy of Texas Instruments, Incorporated.)

### 1.4 HARDWARE ELEMENTS OF THE DIGITAL COMPUTER SYSTEM

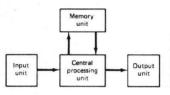

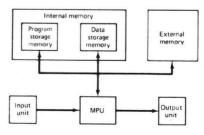

The hardware of a digital computer system is divided into four functional sections. The block diagram of Fig. 1.8 shows the four basic units of a simplified computer: the *input unit*, central processing unit, memory unit, and output unit. Each section has a special function in terms of overall computer operation.

Figure 1.8 Block diagram of a digital computer. (From Walter A. Triebel, Integrated Digital Electronics, © 1979. Adapted by permission of Prentice-Hall, Inc., Englewood Cliffs, N.J.)

The central processing unit (CPU) is the heart of the computer system. It is responsible for performing all arithmetic operations and logic decisions initiated by the program. In addition to arithmetic and logic functions, the CPU controls overall system operation.

On the other hand, the input and output units are the means by which the CPU communicates with the outside world. The *input unit* is used to input information and commands to the CPU for processing. For instance, a Teletype terminal can be used by the programmer to input a new program.

After processing, the information that results must be output. This output of data from the system is performed under control of the *output unit*. Examples of ways of outputting information are as printed pages produced by a high-speed printer or to display it on the screen of a video display terminal.

The *memory unit* of the computer is used to store information such as numbers, names, and addresses. By "store" we mean that memory has the ability to hold this information for processing or for output at a later time. The programs that define how the computer is to process data also reside in memory.

In computer systems, memory is divided into two sections, known as primary storage and secondary storage. They are also sometimes called internal memory and external memory, respectively. External memory is used for long-term storage of information that is not in use. For instance, it holds programs, files of data, and files of information. In most computers, this part of memory employs storage on magnetic media such as magnetic tapes, magnetic disks, and magnetic drums. This is because they have the ability to store large amounts of data.

On the other hand, internal memory is a smaller segment of memory used for temporary storage of programs, data, and information. For instance, when a program is to be executed, its instructions are first brought from external memory into internal memory together with the files of data and information that it will affect. After this, the program is executed and its files updated while they are held in internal memory. When the processing defined by the program is complete, the updated files are returned to external memory. Here the program and files are retained for use at a later time.

The internal memory of a computer system uses electronic memory devices instead of storage on a magnetic-medium memory. In most modern computer systems, semiconductor read-only memory (ROM) and random access read/write memory (RAM) are in use. These devices make internal memory operate much faster than external memory.

Neither semiconductor memory nor magnetic-medium memory alone can satisfy the requirements of most general-purpose computer systems. Because of this fact, both types are normally present in the system. For instance, in a personal computer system, working storage is typically provided with RAM while long-term storage is provided with floppy disk memory. On the other hand, in special-purpose computer systems, such as video games, only semiconductor memory is used. That is, the program that determines how the game is played is stored in ROM, and data storage, such as for graphic patterns, are in RAM.

#### 1.5 GENERAL ARCHITECTURE OF A MICROCOMPUTER SYSTEM

Now that we have introduced the general architecture of a digital computer, let us look at how a microcomputer fits this model. Looking at Fig. 1.9, we find that the architecture of the microcomputer is essentially the same as that of the digital computer shown in Fig. 1.8. It has the same functional elements: input unit, output unit, memory unit, and in place of the CPU, an MPU (microprocessor unit). Moreover, each element serves the same basic functions relative to overall system operation.

Figure 1.9 General microcomputer system architecture.

The difference between minicomputers, mainframe computers, and microcomputers does not lie in the fundamental blocks used to build the computer; instead, it is in the capacity and performance of the electronics used to implement their blocks and the resulting overall system capacity and performance. As indicated earlier, microcomputers are designed with smaller capacity and lower performance than either minicomputers or mainframes.

Unlike mainframe and minicomputers, a microcomputer can be implemented with a small group of components. Again the heart of the computer system is the MPU (CPU) and it performs all arithmetic, logic, and control operations. However, in a microcomputer the MPU is implemented with a single microprocessor chip instead of a large assortment of SSI and MSI logic functions such as in minis and mainframes. Note that correct use of the term "microprocessor" restricts its use to the central processing unit in a microcomputer system.

Note that we have partitioned the memory unit into an internal memory section for storage of active data and instructions and an external memory section for long-term storage. As in minicomputers, the long-term storage medium in a microcomputer is frequently a floppy disk. However, Winchester rigid disk drives are also becoming popular when storage requirements are higher than those provided by floppy disks. In industrial applications, where the environment for the equipment is rugged, bubble memories are also being employed as long-term storage devices.

Internal memory of the microcomputer is further subdivided into program storage memory and data storage memory. Typically, it is implemented with both ROM and RAM ICs. Data, whether they are to be interpreted as numbers, characters, or instructions, can be stored in either ROM or RAM. But in most microcomputer systems, instructions for the program and data, such as look-up tables, are stored in ROM. This is because this type of information does not normally change. By using ROM, its storage is made nonvolatile. That is, if power is lost, the information is retained.

On the other hand, the numerical and character data that are to be processed by the microprocessor change frequently. They must be stored in a type of memory from which they can be read by the microprocessor, modified through processing, and written back for storage. For this reason, data are stored in RAM instead of ROM.

Depending on the application, the input and output sections can be implemented with something as simple as a few switches for inputs and a few light-emitting diodes (LEDs) for outputs. In other applications, for example a personal computer, the input/output (I/O) devices can be more sophisticated devices, such as video display terminals and printers, just like those employed in minicomputer systems.

Up to this point, we have been discussing what is known as a multichip microcomputer system: that is, a system implemented with a microprocessor and an assortment of support circuits such as ROMs, RAMs, and I/O peri-

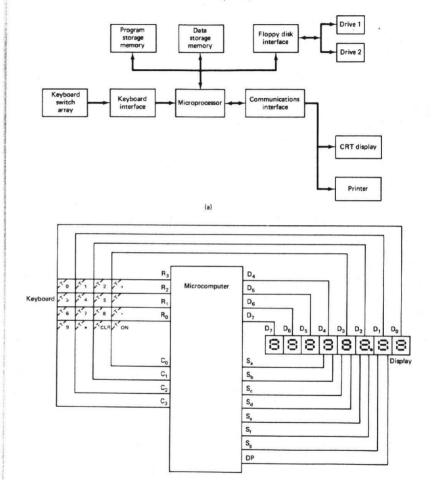

Figure 1.10(a) Block diagram of a personal computer; (b) block diagram of a calculator.

pherals. This architecture makes for a very flexible system design. The system's ROM, RAM, and I/O capacity can easily be expanded by simply adding more devices. This is the circuit configuration used in most larger microcomputer systems. An example is the personal computer system shown in Fig. 1.10(a).

Devices are now being made that include all the functional blocks of a microcomputer in a single IC. This is called a single-chip microcomputer. Unlike the multichip microcomputer, single-chip microcomputers are limited in capacity and are not as easy to expand. For example, a microcomputer device can have 4K (4096; K = 1024) bytes of ROM, 128 bytes of RAM, and 32 lines for use as inputs or outputs. Because of this limited capability, single-chip microcomputers find wide use in special-purpose computer applications. A block diagram of a calculator implemented with a single-chip microcomputer is shown in Fig. 1.10(b).

### 1.6 TYPES OF MICROPROCESSORS AND SINGLE-CHIP MICROCOMPUTERS

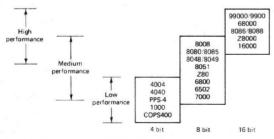

The primary way in which microprocessors and microcomputers are categorized is in terms of the number of binary bits in the data they process: that is, their word length. Figure 1.11 shows that the three standard organizations used in the design of microprocessors and microcomputers are 4-bit, 8-bit, and 16-bit data words.

The first microprocessors and microcomputers, introduced in the early 1970s, were all designed to process data that were arranged 4 bits wide. This organization is frequently referred to as a *nibble* of data. Many of the early 4-bit devices, such as the PPS-4 microprocessor made by Rockwell Interna-

Figure 1.11 Microprocessor and single-chip microcomputer categories and relative performance.

tional and the TMS1000 single-chip microcomputer made by Texas Instruments, are still in wide use today.

The low performance and limited system capabilities of these 4-bit microcomputers limit their use to simpler, special-purpose applications. Some common uses are in calculators and electronic toys. In these types of equipment, low cost, not high performance, is the overriding requirement in the selection of a processor.

In the 1973-1974 period, second-generation microprocessors were introduced. These devices, such as Intel Corporation's 8008 and 8080, were 8-bit microprocessors; that is, they were designed to process 8-bit (one-byte-wide) data instead of 4-bit data.

The newer 8-bit microprocessors exhibited higher-performance operation, larger system capabilities, and greater ease of programming. They were able to provide the system requirements for many applications that could not be satisfied by 4-bit microcomputers. These extended capabilities led to widespread acceptance of multichip 8-bit microcomputers for special-purpose system designs. Examples of some of these dedicated applications are electronic instruments, cash registers, and printers.

Somewhat later, 8-bit microprocessors began to migrate into general-purpose microcomputer systems. In fact, the Z-80A is the host MPU in a number of today's popular personal computers.

Late in the 1970s, 8-bit single-chip microcomputers, such as Intel's 8048, became available. The full microcomputer capability of this single chip further reduced the cost of implementing designs for smaller, dedicated digital systems. In fact, 8-bit microcomputers are still being designed for introduction into today's marketplace. An example is Texas Instruments' new TMS7000 family of 8-bit microcomputers. Newer devices, such as the TMS7000, offer one order-of-magnitude higher performance, more powerful instruction sets, and special on-chip functions such as interval/event timers and universal asynchronous receiver/transmitters (UARTs).

Plans for the development of third-generation (16-bit) microprocessors were announced by many of the leading semiconductor manufacturers in the mid-1970s. The 9900, which was the forerunner of the 99000 that we describe in this book, was introduced commercially in 1977. It was followed by a number of other important devices, such as the 9981, 8086, 8088, Z8000, 68000, and 99000. These devices are all high in performance and have the ability to satisfy a broad scope of special-purpose and general-purpose computer applications. All have the ability to handle 8-bit as well as 16-bit data words. Some can even process data organized as 32-bit words. Moreover, their powerful instruction sets are more in line with those provided by minicomputers than of those associated with 8-bit microprocessors.

In terms of special-purpose applications, 16-bit microprocessors are replacing 8-bit processors in applications that require very high performance:

Chap. 1

Sixteen-bit microprocessors are also being used in applications that can benefit from their extended system capabilities. For instance, they are beginning to be used in word processing systems. This type of system requires a large number of character data to be active temporarily; therefore, it can benefit from the ability of a 16-bit microprocessor to access a much larger amount of data storage memory.

Most new personal computer designs incorporate 16-bit microprocessors. For example, IBM's personal computer and Texas Instruments' home computer use 16-bit microprocessors to implement their microcomputers.

#### ASSIGNMENT

#### Section 1.2

- 1. What guides a computer as to how it is to process data?

- 2. What type of electronic devices are revolutionizing the low-performance, low-cost computer market today?

#### Section 1.3

- 3. What is the principal difference between mainframe, mini-, and microcomputers?

- 4. What is meant by "general-purpose computer"?

- 5. What is meant by "special-purpose computer"?

#### Section 1.4

- 6. What are the building blocks of a general computer system?

- 7. What is the difference between primary and secondary storage?

#### Section 1.5

- 8. What are the basic building blocks of a microcomputer system?

- 9. What is the difference between program storage and data storage memory in a microcomputer?

- 10. What is the difference between internal and external storage memory in a micro-computer?

#### Section 1.6

- 11. What are the standard data word lengths of today's microprocessors and microcomputers?

- 12. What is the difference between a multichip microcomputer and a single-chip microcomputer?

- 13. Name five 16-bit microprocessor families.

## THE 99000 MICROPROCESSOR

#### 2.1 INTRODUCTION

Chapter 1 introduced general aspects of microprocessors and microcomputers. In this chapter we begin a detailed study of the 99000 microprocessor and its architecture. In the chapters that follow, its instruction set, external interfaces (memory, input/output, and interrupt), and special features such as macrostore and privileged mode are presented. The following list outlines the topics that are covered:

- 1. The 99000 microprocessor

- 2. Block diagram of the 99000 microprocessor

- 3. Internal architecture of the 99000 microprocessor

- 4. Instruction execution

#### 2.2 THE 99000 MICROPROCESSOR

The 99000 is one of the higher-performance 16-bit microprocessors available in the marketplace today. As shown in Fig. 2.1, it is the third-generation member of a family of 16-bit microprocessors and microcomputers manufactured by Texas Instruments. The first family member, the 9900, was introduced in 1975. It was followed by a steady stream of new devices, including the 9980 in 1977 and the 9940 in 1979. The second-generation device, the 9995, was introduced in 1980, and the third-generation microprocessor, the 99000. in 1981.

Figure 2.1 Evolution of the 9900/ 99000 family. (Courtesy of Texas Instruments, Incorporated.)

The 9900, 9995, and 99000 devices represent a continuity of hardware and software based on Texas Instrument's memory-to-memory architecture. Even though new family members have been introduced, software compatibility has been maintained for all devices. That is, the instruction sets of the newer devices are just supersets of those performed by the original 9900 microprocessor. Therefore, no modifications are required on software written for the older processors in order to run it on the newer 9995 and 99000 processors.

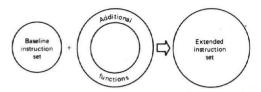

Through the evolution from the first 9900 microprocessor to today's 99000, many enhancements have been made to the features and functionality of the architecture and instruction set. For instance, on-chip memory known as macrostore permits high-speed instruction execution and at the same time permits custom and specialized instruction extensions to the baseline instruction set of the 99000. Moreover, the standard instruction set now includes additions such as signed multiply and signed divide as well as instructions that perform multiprecision arithmetic operations. An example of a hardware enhancement is the extension of the address reach of the 99000 to 256K bytes. It is these kinds of improvements that have resulted in the 99000's high throughput, efficient performance, and flexible system capabilities.

The name "99000" actually represents a family of microprocessors. At present, two family members have been defined. The first device announced, the 99105A, is what is known as the baseline 99000. This means that it does not contain any special-purpose on-chip macrostore. The second family member, the 99110A, is a processor designed for a specialized function. It has the ability to perform floating-point arithmetic operations in addition to the general-purpose capability of the 99105A. The floating-point instructions are built into its internal macrostore memory area. Throughout the book all references to the 99000 imply that we are referencing features of the 99105A that are common to the current family members.

All members of the 99000 family are manufactured using N-channel metal-oxide semiconductor (NMOS) technology. They use a variation on the basic process known as scaled MOS (SMOS), which is a high-performance NMOS technology. It results in a 3-micrometer active device size. The baseline 99000 chip contains approximately 25,000 transistors and when macrostore is added, this is increased to 35,000 transistors.

Sec. 2.3

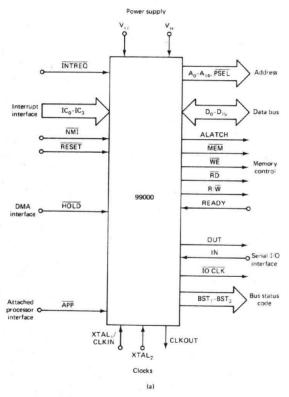

#### 2.3 BLOCK DIAGRAM OF THE 99000 MICROPROCESSOR

Figure 2.2(a) shows a block diagram of the 99000 microprocessor. Here we see that the leads of the device are grouped into the address bus, data bus, memory control lines, bus status lines, serial I/O interface, interrupt interface, DMA interface, attached processor interface, power supply lines, and clock signal lines. In this diagram, we have shown all signal lines to be inde-

Figure 2.2(a) Block diagram of the 99000 microprocessor. (Courtesy of Texas Instruments, Incorporated.)

Figure 2.2(b) Pin layout. (Courtesy of Texas Instruments, Incorporated.)

pendent. However, the 99000 is packaged in a 40-pin package. For this reason, a number of its signals are actually multiplexed.

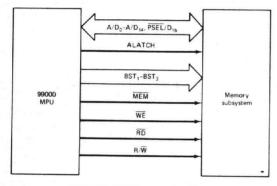

Figure 2.2(b) shows the pin layout of the 99000. Note that the address bus and data bus signals are multiplexed over the same set of lines. These lines are labeled  $A_0/D_0$  through  $A_{14}/D_{14}$ . Furthermore, bit  $D_{15}$  of the data bus is multiplexed with two other signals,  $\overline{PSEL}$  and OUT, at pin 31.

Before going further, let us look briefly at each of these signal groups and their functions.

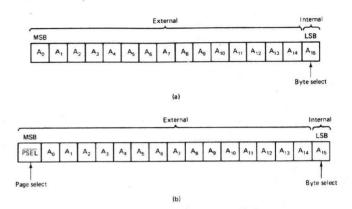

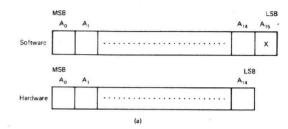

#### Address/Data Bus

The 99000 microprocessor has a 15-bit external address bus. In Fig. 2.2, these lines are labeled  $A_0$  through  $A_{14}$ . The binary information output on this bus is used to specify the storage location that is to be accessed during data transfers between the 99000 and memory, registers within memory-mapped LSI peripherals, and I/O-mapped input/output ports. This is a unidirectional bus. That is, address words are output by the microprocessor only over these signal lines. Signal line  $\overline{PSEL}$  is an additional address bit that is used to extend the address bus to 16 bits.

The data bus consists of 16 lines,  $D_0$  through  $D_{15}$ . This is a bidirectional bus instead of a unidirectional bus. Therefore, its lines are used to carry data into or out of the microprocessor. It is over these lines that data are transferred during memory read or write operations, and for input or output of data for LSI peripherals or other I/O devices.

#### **Memory Control Signals**

A second group of signals in Fig. 2.2 are those labeled as memory control. They tell external memory circuitry whether or not a memory cycle is in progress; if the memory operation is a read or write of data; and the appropriate instants when valid address information, read data, or write data are on the bus.

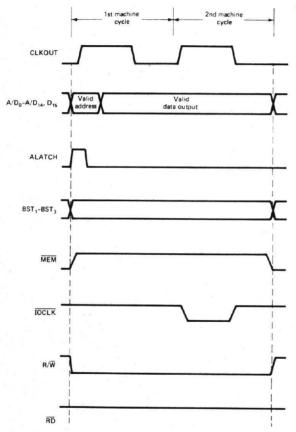

In Fig. 2.3, each memory control signal is listed with its mnemonic, name, and a brief description of its function. Here we find that  $\overline{\text{MEM}}$  (memory cycle) is the signal that indicates to external circuitry in the memory subsystem that a memory cycle is in progress. Moreover, signals ALATCH (address latch),  $\overline{\text{WE}}$  (write enable), and  $\overline{\text{RD}}$  (read enable) identify the moment that a valid address, valid write data, and valid read data, respectively, are on the multiplexed address/data bus.

Another signal is provided in this group to permit use of the 99000 with slow external memory devices. This is the READY signal. Effectively, it gives the ability to extend the bus cycle. That is, after the address is output on the bus, the MPU will wait for the READY signal to be returned from the memory system before it performs the read or write data transfer to complete the memory cycle.

#### Serial Input/Output Interface

The serial input/output (I/O) interface is the bit-addressable input/output path of the 99000. Looking at Fig. 2.2, we see that it consists of three signal lines: OUT,  $\overline{\text{IOCLK}}$ , and IN. These signals are listed in Fig. 2.4 together with

| Mnemonic | Name                 | Function                                                                                         |

|----------|----------------------|--------------------------------------------------------------------------------------------------|

| MEM      | Memory cycle         | 0 indicates that a memory cycle is in progress                                                   |

| WE       | Write enable         | 0 indicates that valid write data is on the data bus                                             |

| ALATCH   | Address latch        | 1 indicates that the multiplexed address/data bus is set up to carry address data                |

| R/W      | Early read/<br>write | 1 indicates that data bus lines will be carrying read<br>data during data phase of the bus cycle |

|          |                      | O indicates that data bus lines will be carrying write data during data phase of the bus cycle   |

| RD       | Read                 | O indicates that a read bus cycle is in progress and that data can be put on the data bus        |

| READY    | Ready                | 1 indicates that the current bus cycle can continue through to completion                        |

|          |                      | indicates that a wait state must be inserted into<br>the current bus cycle                       |

Figure 2.3 Memory control signals.

summaries of their functions. It is these lines that are used to interface with bit-oriented parallel I/O ports and some special-purpose serial-interfaced LSI peripherals.

These three I/O lines provide a bit-serial input/output mechanism. Bits of data are output in serial form over the OUT (data output) line synchronously with clock pulses at the  $\overline{\text{IOCLK}}$  (I/O clock) line. Bit-serial data are input at IN (data input).

During a bit-serial I/O operation, the I/O ports to which serial bits of data are sent or from which they are received are identified by I/O addresses instead of memory addresses. These addresses are also output on the system address bus,  $A_0$  through  $A_{14}$ . They are used either to control external multiplexing and decoding circuits that channel the bits of data output at OUT to the appropriate output port, or to select data from specific input ports and pass them onto the IN line.

| Mnemonic | Name               | Function                                                   |  |

|----------|--------------------|------------------------------------------------------------|--|

| IOCLK    | Input/output clock | pulsed to logic 0 as each bit of bit-serial data is output |  |

| OUT      | Data output        | data output for the bit-serial I/O interface               |  |

| IN       | Data input         | data input for the bit-serial I/O interface                |  |

Figure 2.4 I/O signals.

#### Status Bus and Bus Status Codes

The 99000 outputs codes on status bus lines  $BST_1$  through  $BST_3$  which identify the type of bus cycle that is being executed. Figure 2.5 is a list of the mnemonics and names of the 16 types of bus status codes. These codes, together with the  $\overline{MEM}$  signal, indicate to external circuitry whether the MPU is performing a memory cycle, internal cycle, I/O cycle, or special function such as a hold-state acknowledge or interrupt acknowledge. They are decoded in external circuitry to produce control signals for demultiplexing the address, data, and serial I/O buses.

Notice that the codes repeat for the 0 and 1 logic levels of  $\overline{\text{MEM}}$ . The group where  $\overline{\text{MEM}}=0$  corresponds to memory cycles. For example, the instruction acquisition (IAQ) code BST<sub>1</sub>BST<sub>2</sub>BST<sub>3</sub> = 011 indicates that an instruction is being fetched over the data bus.

The other group, which occurs with  $\overline{\text{MEM}}=1$ , corresponds to internal cycles and special functions such as IO, HOLDA, and RESET. An example is the IO code 011, which signals that an I/O operation is taking place.

| MEM | BST, | $BST_2$ | BST <sub>3</sub> | Mnemonic | Name                          |

|-----|------|---------|------------------|----------|-------------------------------|

| 0   | 0    | 0       | 0                | SOPL     | Source operand with MPILCK    |

| 0   | 0    | 0       | 1                | SOP      | Source operand                |

| 0   | 0    | 1       | 0                | IOP      | Immediate operand             |

| 0   | 0    | 1       | 1                | IAQ      | Instruction acquisition       |

| 0   | 1    | 0       | 0                | DOP      | Destination operand           |

| 0   | 1    | 0       | 1                | INTA     | Interrupt acknowledge         |

| 0   | 1    | 1       | 0                | ws       | Workspace                     |

| 0   | 1    | 1       | 1                | GM       | General memory                |

| 1   | 0    | 0       | 0                | AUMSL    | ALU or macrostore with MPILCI |

| 1   | 0    | 0       | 1                | AUMS     | ALU or macrostore             |

| 1   | 0    | 1       | 0                | RESET    | Reset                         |

| 1   | 0    | 1       | 1                | IO       | Input/output                  |

| 1   | 1    | 0       | 0                | WP       | Workspace pointer             |

| 1   | 1    | 0       | 1                | ST       | Status register               |

| 1   | 1    | 1       | 0                | MID      | Macroinstruction detect       |

| 1   | 1    | 1       | 1                | HOLDA    | Hold acknowledge              |

Figure 2.5 Bus status codes. (Courtesy of Texas Instruments, Incorporated.)

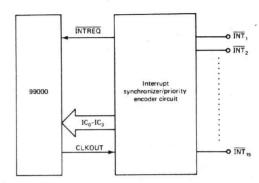

#### Interrupt Interface

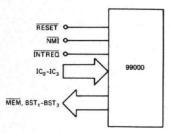

The interrupt interface is used to signal the 99000 that an external device is requesting service. There are three types of hardware interrupt inputs on the 99000: the reset function, nonmaskable interrupt, and external user-definable interrupts.

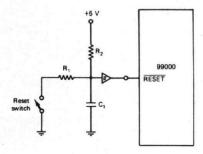

The signal lines of the interrupt interface are listed in Fig. 2.6. The  $\overline{\text{RESET}}$  (reset) interrupt input is used as a hardware initialization input to the microprocessor. On the other hand, the  $\overline{\text{NMI}}$  line represents the non-maskable interrupt input. It is typically used to implement a nonmaskable service request for an external device. The other five lines,  $\overline{\text{INTREQ}}$  and  $\text{IC}_0$  through IC3, represent a prioritized maskable interrupt interface. They can be used to implement user-defined interrupt requests. Signal  $\overline{\text{INTREQ}}$  is used to tell the 99000 that a valid code is present, while the binary combination at IC0,IC1,IC2,IC3 identifies the priority level of the external device that is requesting service.

| Mnemonic                                                        | Name                  | Function                                                                  |

|-----------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------|

| INTREQ                                                          | Interrupt request     | O signals that an external device is requestin<br>service by an interrupt |

| IC <sub>0</sub> IC <sub>1</sub> IC <sub>2</sub> IC <sub>3</sub> | Interrupt code        | code that identifies the external device requesting service               |

| NMI                                                             | Nonmaskable interrupt | 0 indicates that the nonmaskable interrupt is active                      |

| RESET                                                           | Reset                 | 0 indicates that the hardware reset function is active                    |

Figure 2.6 Interrupt interface signals.

#### **Direct Memory Access Interface**

The DMA (direct memory access) interface, which is identified in Fig. 2.2(a), is used to put the 99000 into what is known as the hold state. In this state, the microprocessor gives up control of the system bus. It does this by putting the address/data bus and control lines into the high-Z (high-impedance) state and then suspending operation. In this way, an external device such as a DMA controller can take control of the system bus and has the ability to access directly the memory subsystem of the microcomputer.

The HOLD line is for input of the external signal that is used to initiate transition to the hold state. When the 99000 enters this state, it acknowleges this fact to external circuitry by outputting a HOLDA (hold acknowledge) code on the status bus.

#### **Attached Processor Interface**

The attached processor interface corresponds to the signal line APP (attached processor present) in the block diagram of Fig. 2.2(a). The APP signal indicates to the 99000 that an attached processor in the system is ready to perform a function. In response, the 99000 suspends operation and passes control to the attached processor. The attached processor performs the required function and then returns control to the 99000.

#### Clock Signals

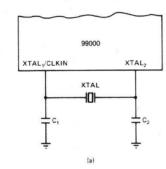

The 99000 contains internal clock drive circuitry. Therefore, to operate, it needs only an external crystal. The crystal is attached between the XTAL, and XTAL, leads as shown in Fig. 2.7(a). Note that shunt capacitors are required from each of these terminals to ground. C1 and C2 each have a typical value of 5 pF. The maximum rating for the crystal is 24 MHz.

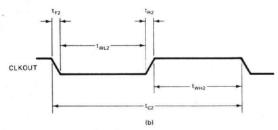

Figure 2.7(a) Crystal connection; (b) CLKOUT waveform. (Courtesy of Texas Instruments, Incorporated.)

Internally, the 24-MHz clock frequency is divided by 4 to give 6-MHz internal operation. This corresponds to a machine cycle time of

$$t_{\text{cycle}} = \frac{1}{6 \text{ MHz}} = 167 \text{ ns}$$

This time is also known as the machine state time of the 99000. The mini-

mum duration that an external bus cycle requires is one machine state, or 167 ns.

The 6-MHz system clock is provided as an output at the CLKOUT line. Figure 2.7(b) shows this waveform. Notice that the cycle time of CLKOUT is labeled to and has a nominal value of 167 ns. Its one-level pulse width twH2 and zero-level pulse width twL2 both have a typical value of 73.5 ns. The rise and fall time between the 0 and 1 levels are called tR2 and tF2, respectively, and have the identical maximum value of 15 ns. This signal is provided for use in synchronizing the operation of external circuitry to that of the 99000 MPU.

If preferred, operation of the 99000 can be synchronized to an externally produced clock signal instead of generating it internally. This is done by applying the clock signal to the CLKIN input.

#### 2.4 INTERNAL ARCHITECTURE OF THE 99000 MICROPROCESSOR

Now that we have introduced the 99000 microprocessor and looked briefly at its interface signals, let us proceed by examining its internal architecture.

#### Functional Blocks of the 99000

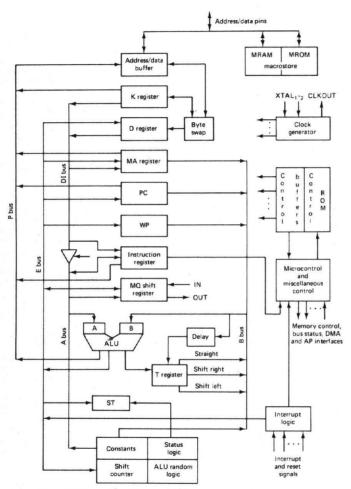

Figure 2.8 shows the internal architecture of the 99000. Here we find that its key sections are the arithmetic-logic unit, internal registers, microcontrol and control ROM, interrupt logic, MQ shift register, clock generator, and macrostore

The arithmetic-logic unit (ALU) is the heart of the 99000 microprocessor. It is responsible for performing the mathematical operations or logical decisions that are required during the execution of an instruction. Notice that it has two inputs, A and B. The ALU takes these inputs and performs a mathematical operation on them such as addition or subtraction or a logical operation such as OR, AND, or exclusive-OR. The result of this operation is provided at the output of the ALU. The ALU has the ability to perform operations on either bytes or words of data.

The internal registers of the CPU are used to store data and status required by the MPU. For instance, the instruction register is used to store the operation code (opcode) of the instruction that is being executed.

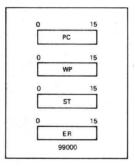

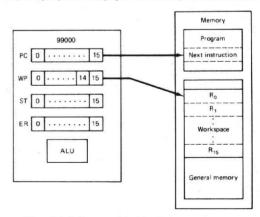

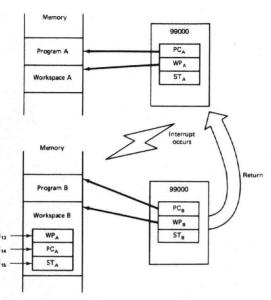

Three of the most important registers within the 99000 are its program counter (PC), workspace pointer (WP), and status register (ST). They are called user-accessible registers. This is because their contents can be loaded or saved under software control.

The microcontrol and control ROM sections are used to decode the instruction operation code that is held in the instruction register. Based on

Figure 2.8 Internal architecture of the 99000. (Courtesy of Texas Instruments, Incorporated.)

this decoding, it outputs the buffered control signals. These signals control the sequence in which the 99000 performs internal and external operations such that the function specified in the instruction is performed.

The interrupt logic identifies that an external device is requesting service by the MPU through the interrupt interface. It indicates this fact to the microcontrol section.

The MQ shift register is the most important part of the serial I/O interface. It does the serial-to-parallel conversion required for input operations and parallel-to-serial conversion required for output operations.

The circuitry in the *clock driver* block generates the 6-MHz four-phase clock signals required by the 99000. These signals synchronize the internal and external operations of the 99000.

The last section, the *macrostore*, is an internal memory area of the 99000. It consists of a *macro-RAM* (MRAM) data storage section and a mask-programmable *macro-ROM* (MROM) instruction storage section. The purpose of macro-ROM is for on-chip storage of *macroinstruction emulation routines*. Typically, macroinstruction emulation routines are used to extend the instruction set of the 99000. This is done by implementing more complex functions, such as special instructions for floating-point arithmetic.

#### Memory-to-Memory Architecture

Sec. 2.4

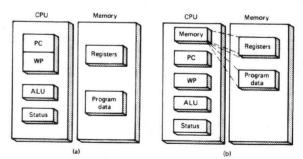

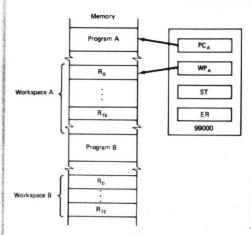

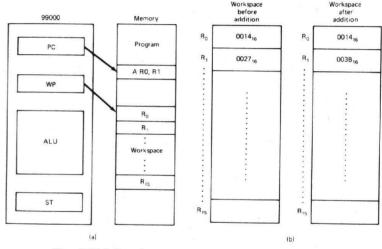

The memory-to-memory architecture is unique in that all of the registers used by the MPU for data operations and addressing are in external memory instead of internal to the device. This type of architecture is illustrated in Fig. 2.9(a). Moreover, these registers are simply memory locations and not random logic circuits such as those used in register-based microprocessor architectures.

Figure 2.9(a) Memory-to-memory architecture; (b) memory-to-memory architecture with on-chip memory. (Courtesy of Texas Instruments, Incorporated.)

The important benefit of using memory instead of random logic for the registers of the MPU is that memory can be integrated more compactly. Memory registers can be moved onto the chip to be more consistent with traditional microprocessor architectures. However, because of the more compact nature of memory, a larger number of registers can be implemented. An example of a microprocessor that employs an on-chip register file is the 9995. The macrostore section of the 99000 is another example of on-chip memory. Its architecture is shown in Fig. 2.9(b).

#### **User-Accessible Registers**

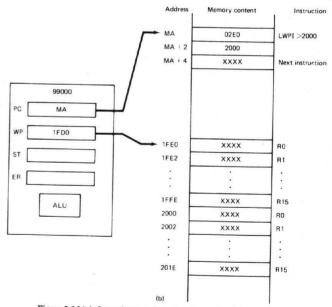

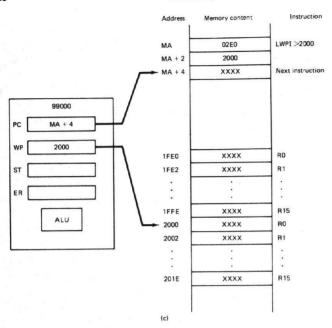

As indicated earlier, by "user-accessible registers" we mean those registers whose contents can be accessed and altered through software. Figure 2.10 shows that the 99000 has just four of these registers: the program counter (PC), workspace pointer (WP), status register (ST), and error register (ER).

Figure 2.10 User-accessible registers.

Figure 2.11 shows the relationship between the internal registers of the 99000. The program counter (PC) is a 16-bit register that contains the address of the next instruction in the program that is to be fetched for execution or the address of an immediate operand that is required during execution of the current instruction. Actually, the least significant bit (LSB) of PC is always zero. This is because instructions are always accessed as words. The value in PC is multiplexed onto the address/data bus during the address phase of an instruction-acquisition bus cycle. The instruction word stored at this location in program storage memory is put on the data bus. During the data-transfer part of the bus cycle, the 99000 reads the word and stores it in its instruction register. After this, the value in PC is automatically incremented by 2 such that it points to the next instruction or operand of the program.

Figure 2.11 Relationship between the user-accessible registers. (Courtesy of Texas Instruments, Incorporated.)

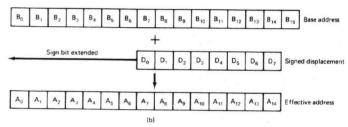

On the other hand, the workspace pointer (WP) contains a 16-bit address that points to the first register in a block of 16 registers in data storage memory. These registers are also identified in Fig. 2.11. They serve as source and destination registers of data operands, address registers, or index registers. The LSB of this address is also always zero.

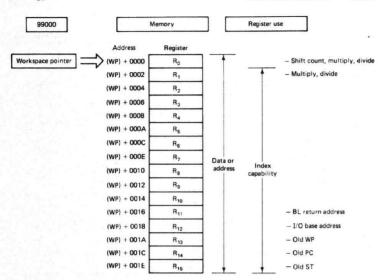

In Fig. 2.12, the 16-register workspace is shown in more detail. Here we see that the registers are labeled  $R_0$  through  $R_{15}$ . Notice also that they are located at addresses that are displaced from the value in WP. The displacement value equals twice the register number. For instance, register  $R_2$  is at address WP + 2(2) = WP + 4.

#### Example 2.1

Find the address of register  $R_{15}$  relative to the workspace pointer. Assume that the workspace pointer contains  $F000_{16}$ . Express the result in hexadecimal form.

Solution: Adding twice the register number to the contents of WP, we get

$$(WP) + 15(2)$$

$(WP) + 30$

Now replacing (WP) with  ${\rm F000_{16}}$  and expressing 30 in hexadecimal form gives the address of register 15 as

$$F000_{16} + 1E_{16} = F01E_{16}$$

Any of these 16 workspace registers can be used for the storage of data or addresses; however, some also have dedicated functions. For example,

Figure 2.12 Workspace registers. (Courtesy of Texas Instruments, Incorporated.)

registers  $R_{13}$ ,  $R_{14}$ , and  $R_{15}$  are used to save the old values of the workspace pointer, program counter, and status register, respectively, when a context switch initiates a change in program environment. Other examples are: register  $R_{12}$ , which is required for storage of a CRU base address for use in I/O operations; register  $R_{11}$ , which is reserved for storage of a return address when a "branch and link" (subroutine) instruction is executed; and register  $R_0$ , which is needed for storage of a shift count for some instructions.

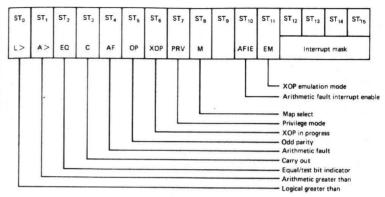

The status register (ST) is another 16-bit internal register of the 99000. Figure 2.13 shows the individual bits of this register and their meanings. Notice that a number of these bits specify conditions that result during the execution of an instruction. Other bits are used to enable or disable functional capabilities of the 99000.

Bits in the group from  $ST_0$  through  $ST_6$  are those that are affected by the execution of instructions. These bits are either set or reset based on the results produced due to the execution of an instruction. For example, after the execution of an addition instruction, we might find changes in A > (arithmetic greater than), EQ (equal), and C (carry). However, it should be noted that not all instructions affect these status bits.

Figure 2.13 Status register.

Some instructions of the 99000 can be used to examine the status of specific bits in the status register and perform certain operations based on whether they are set or reset. An example is the "jump on equal" instruction (JEQ). It tests to see if the equal bit is set. If EQ is found to be set, a jump is initiated to another instruction located at a displaced PC value. Otherwise, the instruction at the next sequential value of PC is executed.

#### Example 2.2

Which of the status bits would you expect to be affected by an instruction that compares two operands?

Solution: The result of an operand comparison would be the fact that one is greater than, less than, or equal to the other. For this reason, we would expect changes in  $ST_0$  through  $ST_2$ : logical greater than (L>), arithmetic greater than (A>), and equal (EQ).

Bits  $ST_7$  through  $ST_{11}$  of the status register are those that enable or disable optional functions of the 99000. Examples are:  $ST_{10}$ , which is used to enable what is known as the automatic arithmetic overflow detection mechanism, and  $ST_7$ , which enables the nonprivileged mode of operation. These status bits must be set to the 1 logic level to perform their identified functions. For instance, setting PRV to 1 enables the nonprivileged mode of operation, and clearing it disables the nonprivileged mode.

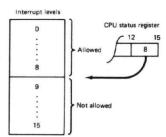

The four least significant bits of the status register,  $ST_{12}$  through  $ST_{15}$ , hold an *interrupt mask code*. It always contains a 4-bit value equal to one less than that of the priority level of the currently active interrupt. In turn, all interrupts with lower priority are disabled from operating.

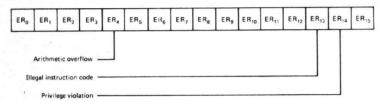

The last of the 99000's user-accessible registers is the error register (ER). Figure 2.14 shows that just three of its bits are internally implemented. These bits represent internal conditions that are considered to be errors when they occur within the 99000. For instance, if an arithmetic overflow occurs and this option is enabled through status bit ST<sub>10</sub>, the error condition is flagged by automatically setting ER<sub>4</sub> to logic 1. This bit location can then be examined through software to identify the fact that an overflow has occurred.

Figure 2.14 Error register.

The other two implemented bits of the error register, ER<sub>13</sub> and ER<sub>14</sub>, represent the detection of an illegal instruction opcode during the execution of the program and the occurrence of a privileged mode violation.

#### Example 2.3

What condition must exist in the status register before bit  $ER_{14}$  can be set due to the occurrence of a privileged mode violation?

Solution: The nonprivileged mode of operation must be enabled by setting PRV (status bit  $ST_7$ ) to logic 1.

#### 2.5 EXECUTION OF AN INSTRUCTION

Now that we have introduced the 99000 and its memory-to-memory architecture, let us continue by considering how it executes an instruction. As indicated in Section 2.4, the primary difference between register architecture and memory-to-memory architecture lies in the fact that memory-to-memory processors, such as the 99000, perform all operations directly on data operands in memory. Here we will describe in detail the effect of executing an addition instruction, the microstates that are performed during execution of the instruction, the 99000's instruction prefetch mechanism, and bus status codes.

#### **Execution of an Addition Instruction**

Execution of an Instruction

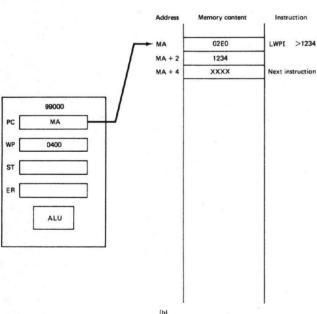

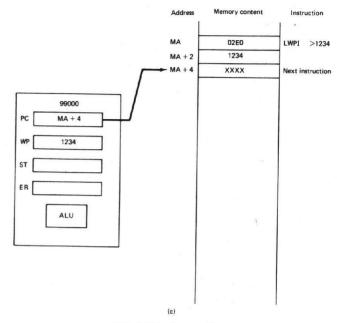

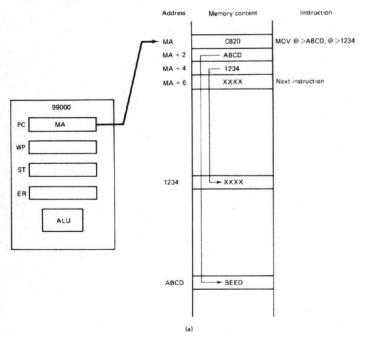

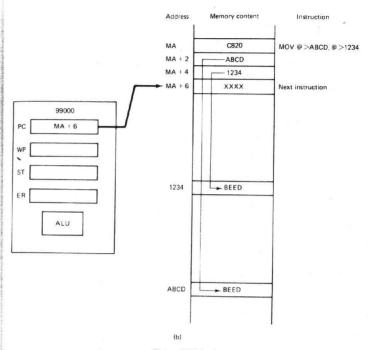

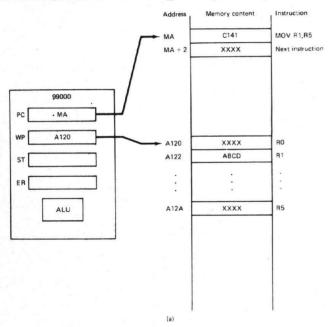

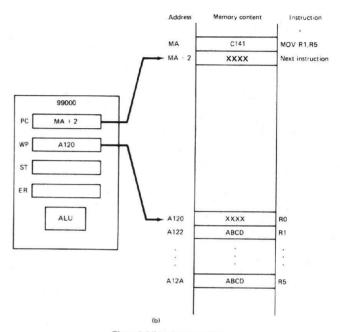

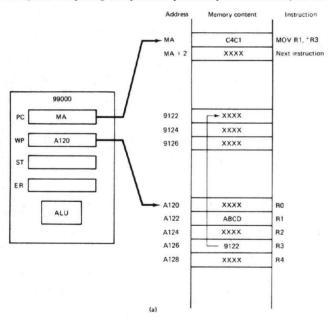

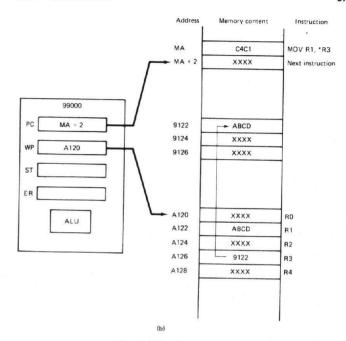

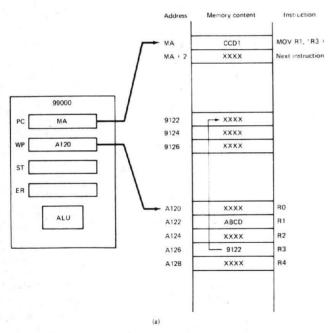

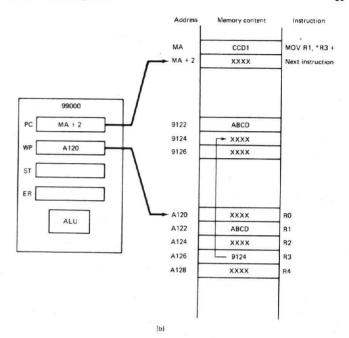

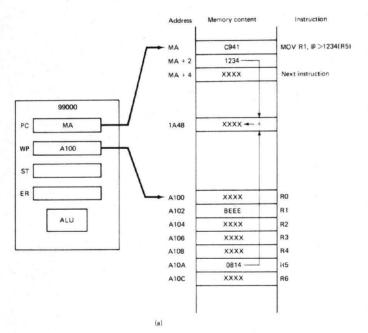

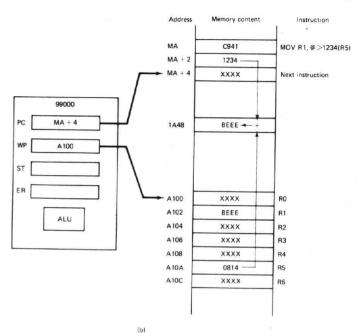

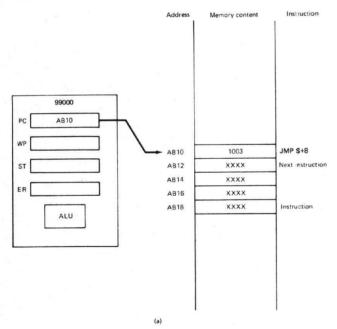

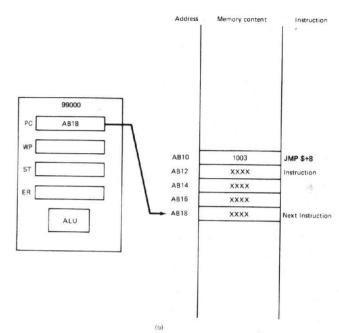

Figure 2.15(a) illustrates the execution of an instruction. Notice that the program counter points in program memory to the instruction

#### A RO.R1

This instruction represents the addition of a source operand that is stored in workspace register  $R_0$  to a destination operand that is located in register  $R_1$ . Their sum, which equals the original contents of  $R_0$  plus the original contents of  $R_1$ , is returned to destination register  $R_1$ .

Figure 2.15(a) Execution of an instruction; (b) workspace registers before and after execution of the addition instruction. (Courtesy of Texas Instruments, Incorporated.)

The example in Fig. 2.15(b) indicates that before the addition instruction occurs,  $R_0$  contains the data word  $0014_{16}$  and  $R_1$  contains  $0027_{16}$ . Executing the add word instruction creates the sum

$$0014_{16} + 0027_{16} = 003B_{16}$$

and stores this value in R<sub>1</sub>. The value held in R<sub>0</sub> remains unchanged. These results are shown in Fig. 2.15(b).

#### Steps in the Addition Instruction

34

The execution of an instruction actually requires the 99000 to go step by step through a series of internal and external operations. This sequence of events is microcoded into the control ROM section. When an instruction is fetched from program memory, it is loaded into the instruction register within the 99000. The microcontrol section decodes the opcode and initiates the appropriate microcode sequence. The control ROM outputs signals that are used to sequence and time the internal operations, and external bus operations that are required to perform the processing specified by the instruction.

The actual sequence of operations that occur during the execution of the instruction

#### A R0 R1

is shown in Fig. 2.16(a). Notice that there are six operations, of which four are memory bus cycles and two are internal cycles. The sequence begins with an instruction acquisition memory bus cycle. During this cycle, the instruc-

| Step | Function                    | Type     |

|------|-----------------------------|----------|

| 1    | Fetch instruction           | Memory   |

| 2    | Decode instruction          | Internal |

| 3    | Fetch source operand        | Memory   |

| 4    | Fetch destination operand   | Memory   |

| 5    | Add operands                | Internal |

| 6    | Write result to destination | Memory   |

| Instruction fetch |                   |                   |

|-------------------|-------------------|-------------------|

| Decode            |                   |                   |

| Source fetch      |                   |                   |

| Destination fetch |                   |                   |

| Process           | Instruction fetch |                   |

| Write             | Decode            |                   |

|                   | Source fetch      |                   |

|                   | Destination fetch |                   |

|                   | Process           | Instruction fetch |

|                   | Write             | Decode            |

|                   | 121               | Source fetch      |

|                   |                   |                   |

Figure 2.16(a) Register-to-register addition sequence; (b) prefetch mechanism. (Courtesy of Texas Instruments, Incorporated.)

tion is fetched from the program memory. The instruction is loaded into the instruction register of the microprocessor. This represents the instruction fetch part of the instruction acquisition cycle.

The execution phase begins with an internal operation during which the instruction is decoded and the appropriate microcode sequence initiated. The microcode sequence next performs a workspace memory bus cycle during which the source operand is read from source register Ro. This operand is applied to the A input of the ALU. After this, a second workspace memory bus cycle is initiated to read the destination operand from destination register R<sub>1</sub>. It is applied to the B input of the ALU.

Now the microprocessor has the data that it needs and is ready to perform the addition operation. This processing of operands represents the second internal operation shown in Fig. 2.16(a). The add operation is performed and the sum is obtained. The result must now be returned to destination register R, in memory. For this reason, a workspace write bus cycle is initiated

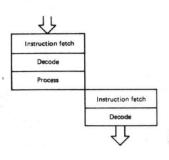

#### Intelligent Prefetch Mechanism

Looking at the instruction sequence in Fig. 2.16(a), we see that during the two internal operations the system bus to external memory is not busy. To make more efficient use of the system bus, the 99000 is implemented with an intelligent instruction prefetch mechanism. With this mechanism, the execution of consecutive instructions is overlapped. This feature is also known as pipelining.

Figure 2.16(b) illustrates how the prefetch mechanism works. Notice that while the first instruction is being processed, the 99000 initiates an instruction acquisition memory bus cycle to fetch the next instruction. This second instruction is decoded while the results from the first instruction are being written to memory. In this way, we see that during each of the six steps of the addition instruction, the system bus is in use. This effectively eliminates any overhead due to the instruction acquisition part of the instruction execution cycle, thereby decreasing the amount of time it takes to execute an instruction. The results of prefetching instructions are improved system throughput, more efficient use of the system bus, and expansion of the bus bandwidth.

Earlier we said that the prefetch mechanism of the 99000 is intelligent. This is because it has the ability to detect automatically whether or not the present instruction is a branch or a jump type of instruction and can calculate the new program counter value before another instruction is fetched. Instead of fetching the next sequential instruction and then having to discard it, the program counter has already been modified such that the new instruction specified by the branch or jump is read and executed. This microcode sequence is shown in Fig. 2.17.

Execution of an Instruction

Figure 2.17 Prefetch sequence for the jump instruction.

#### Bus Status Codes of the Addition Instruction

During each step of the instruction execution sequence, a bus status code is output on status bus lines MEM and BST, through BST,. As shown earlier, the 4 bits of this code are organized as MEMBST, BST, BST, and the code indicates to external circuitry what type of operation is being performed by the 99000.

To understand this idea better, let us look at the bus status codes that occur during execution of the addition instruction we have been using as an example. The internal and external operations that take place during the execution of the register-to-register addition instruction are shown in Fig. 2.18(a). Notice that during step 1 the addition instruction is fetched from memory. This represents an instruction acquisition bus cycle and is accompanied by the IAQ code, which equals 0011, on the status bus.

Step 2 corresponds to the decoding of the addition instruction. This is an internal operation. But at the same time an external bus operation is performed to write the results of the previous instruction to memory. It is this destination write that determines which bus status code is output. Since we have not indicated what type of instruction this was, its mnemonic and status code are represented by a don't know state (X).

During the next two steps, the source and destination operands are fetched from memory. Since the data are stored in registers Ro and Ro of the workspace, their data bus cycles are accompanied by the workspace transfer (WS) bus status code, 0110.

The next operation corresponds to the internal addition of the two operands. A memory operation is also performed during this interval to prefetch the next instruction. Therefore, it is again accompanied by the IAQ code. During the last step, the new instruction is decoded and the results of

| Step | Internal                            | External                                      | Status code name | Status code |

|------|-------------------------------------|-----------------------------------------------|------------------|-------------|

| 1    | Process previous instruction        | *Fetch addition instruction                   | DAI              | 0011        |

| 2    | Decode addition instruction         | Write result of previous instruction          | xxx              | xxxx        |

| 3    |                                     | *Read source operand for add instruction      | ws               | 0110        |

| 4    |                                     | *Read destination operand for add instruction | ws               | 0110        |

| 5    | Add source and destination operands | Fetch next instruction                        | DAI              | 0011        |

| 6    | Decode next instruction             | *Write result of addition to destination      | ws               | 0110        |

\*Memory cycles associated with the addition instruction

| Step | Internal                     | External                              | Status code name | Status code |

|------|------------------------------|---------------------------------------|------------------|-------------|

| 1    | Process previous instruction | Fetch jump instruction                | DAI              | 0011        |

| 2    | Decode jump instruction      | Write results of previous instruction | xxx              | xxxx        |

| 3    | Process jump instruction     | No operation                          | AUMS             | 1001        |

| 4    | No operation                 | Fetch instruction from new location   | IAQ              | 0011        |

| 5    | Decode new instruction       | No operation                          | AUMS             | 1001        |

(b)

Figure 2.18(a) Status codes for the addition instruction execution sequence; (b) status codes for execution of the jump instruction.

the addition instruction are written to memory. The destination register R<sub>1</sub> is in the workspace; therefore, the WS bus status code is again output.

The bus status codes that are output during a jump instruction are shown in Fig. 2.18(b). In this case, the 99000 processes the instruction immediately after decoding. During this time, no bus activity takes place; therefore, the internal arithmetic logic unit bus status code AUMS = 1001 is output. This is followed by the fetch of an instruction from the new address location accompanied by bus status code IAQ = 0001. Finally, the new instruction is decoded without an external bus cycle occurring for the jump instruction. This gives another AUMS = 1001 bus status code.

#### **ASSIGNMENT**

#### Section 2.2

- 1. Name the technology used to fabricate the 99000 family of microprocessors.

- 2. Name three advanced features of the 99000 that are not available on the older 9900 microprocessor.

- 3. What is meant by "macrostore"?

- 4. What is the main distinction between the 99105A and 99110A devices?

#### Section 2.3

- 5. What is the size of the 99000's package?

- 6. Which lines are used to output memory addresses?

- 7. Which lines form the data bus?

- 8. What function is served by the READY input?

- 9. Which line is used to input data during a serial input operation?

- 10. What lines are involved in the selection and output of data to an output port if the output operation is performed through the serial output interface?

- 11. What function is served by the bus status lines?

- 12. How many maskable interrupts are allowed in a 99000 system?

- 13. How does the 99000 acknowledge a DMA request?

#### Section 2.4

- 14. What are the three main user-accessible registers of the 99000?

- 15. What is the function of the ALU?

- 16. What function is served by microcontrol and the control ROM?

- 17. Which register is involved in serial I/O operations?

- 18. Specify the purpose of both MRAM and MROM.

- 19. What is meant by a memory-to-memory architecture? How does it differ from a register-based microprocessor architecture?

- 20. What function is served by the program counter?

- 21. Explain the function of the workspace pointer.

- 22. If the WP is loaded with 2000<sub>16</sub>, identify each of the workspace registers and give their addresses.

- 23. Which workspace registers do not have an associated dedicated function?

- 24. What is the purpose of the status register?

- 25. Why is an error register provided within the 99000?

#### Section 2.5

- 26. After an instruction is fetched, which part of the processor initiates its execution

- 27. Define "prefetch mechanism." How does it affect the processor's speed of program execution?

- 28. What signals are used by the processor to identify external memory operations during an instruction's execution? Which lines carry these output signals?

# 3

# 99000 MICROPROCESSOR PROGRAMMING I

#### 3.1 INTRODUCTION

Having introduced the architecture of the 99000 microprocessor in Chapter 2, we are now ready to begin investigating its instruction set and some elementary programming concepts. In this chapter we begin by developing a software model of the 99000. This is followed by material that introduces the concepts of assembly language and machine language together with the symbols, notations, and formats used when coding them. Next, the addressing modes of the 99000 are described and their functions demonstrated. After this, we take our first look at the instruction set of the 99000. The data transfer, arithmetic, logical, and shift instructions are described in detail. The topics are presented in the following order:

- 1. Software model of the 99000

- 2. Assembly and machine languages

- 3. Instruction execution notations

- 4. Addressing modes

- 5. Instruction set

- 6. Data transfer instructions

- 7. Arithmetic instructions

- 8. Logic instructions

- 9. Shift instructions

#### 3.2 SOFTWARE MODEL OF THE 99000 MICROPROCESSOR

The purpose of developing a software model is to aid the programmer in understanding the operation of the microcomputer system from a software point of view. To be able to program a microprocessor, one does not need to know all of its hardware features. For instance, we do not necessarily need to know the function of the signals at its various pins, their electrical connections, or their switching characteristics. Moreover, the function, interconnection, and operation of the internal circuits of the microprocessor also need not normally be considered.

What is important to the programmer is to know the various registers within the device and understand their purpose, functions, and operating capabilities and limitations. Furthermore, it is essential to know how external memory is organized and how it is addressed to obtain instructions and data.

A software model for the 99000 that includes its internal registers and external memory area is illustrated in Fig. 3.1. Looking at this model, we find four internal registers: the program counter (PC), workspace pointer (WP), status register (ST), and error register (ER). Each of these registers was discussed in detail in Chapter 2. For this reason, let us simply review them briefly here. This time we will concentrate on their relationship to software.

The program counter is a 16-bit register that produces word addresses for accessing the program storage part of memory. From a software point of

Figure 3.1 Software model of the 99000 microprocessor.

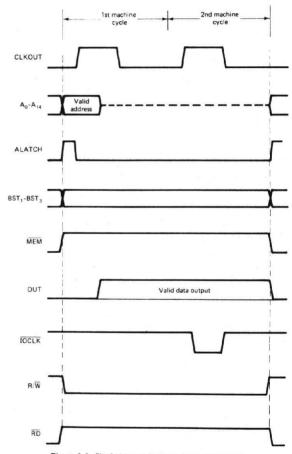

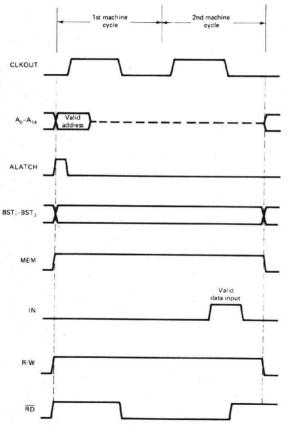

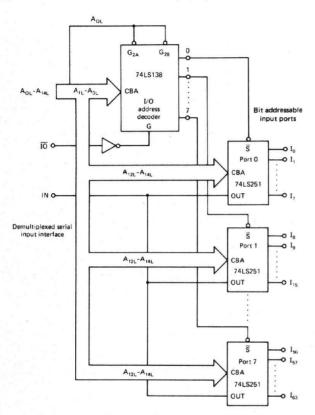

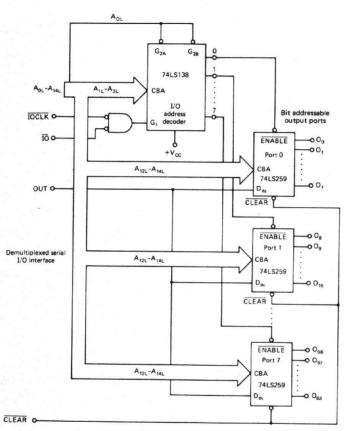

view, we must know that at any instant the contents of PC represent the address of the next instruction that is to be fetched for execution, or immediate data for the current instruction. In this way, we see that it determines the sequence in which instructions are executed.